Year after year, the explosive growth of computing power relies on manufacturers’ ability to fit more and more components into the same amount of space on a silicon chip. That progress, however, is now approaching the limits of the laws of physics, and new materials are being explored as potential replacements for the silicon semiconductors long at the heart of the computer industry.

New materials may also enable entirely new paradigms for individual chip components and their overall design. One long-promised advance is the ferroelectric field-effect transistor, or FE-FET. Such devices could switch states rapidly enough to perform computation, but also be able to hold those states without being powered, enabling them to function as long-term memory storage. Serving double duty as both RAM and ROM, FE-FET devices would make chips more space efficient and powerful.

The hurdle for making practical FE-FET devices has always been in manufacturing; the materials that best exhibit the necessary ferroelectric effect aren’t compatible with techniques for mass-producing silicon components due the high temperature requirements of the ferroelectric materials.

Now a team of researchers at the University of Pennsylvania School of Engineering and Applied Science has shown a potential way around this problem. In a pair of recent studies, they have demonstrated that scandium-doped aluminum nitride (AlScN), a material recently discovered to exhibit ferroelectricity, can be used to make FE-FET as well as diode-memristor-type memory devices with commercially viable properties.

The studies were led by Deep Jariwala, assistant professor in Electrical and Systems Engineering (ESE), and Xiwen Liu, a graduate student in his lab. They collaborated with fellow Penn Engineering faculty members Troy Olsson, also an assistant professor in ESE, and Eric Stach, professor in the Department of Materials Science and Engineering and Director of the Laboratory for Research on the Structure of Matter.

They published their findings in the journals Nano Letters and Applied Physics Letters.

“One of the main ways that chip designers are thinking about getting around the looming limitations of processing vast amounts of data with silicon is finding materials that would allow memory components to be built directly on top of the processor without harming the processor in the process, essentially making two-in-one devices,” says Jariwala. “Since AlScN can be deposited at relatively low temperatures, we knew it represented a possibility for directly combining memory with logic transistors. We just needed a way to integrate it with the rest of the chip architecture.”

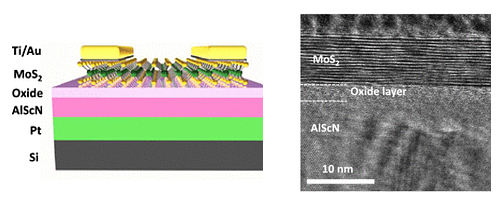

Jariwala and his colleagues found a solution in a promising two-dimensional material known as molybdenum disulfide, or MoS2. Using a single layer of MoS2 as a channel out of an AlScN-based FE-FET device, the team was able to test its switching speed and memory stability. Those results were published in their Nano Letters paper.

“Engineers have been pursuing the concept of FE-FET memory since the 60s, since these devices could operate at extremely low powers,” says Jariwala. “The issue really has been to make their fabrication compatible with processors and make them last longer. This is where our 2D materials come in; they are so thin that once a memory bit is written in them, they could preserve that information in the form of charge for years.”

Jariwala and his colleagues’ next steps were to shrink the dimensions of their memory devices. In their Applied Physics Letters paper, they demonstrated the ability to produce AlScN as thin as 20 nanometers, reducing the overall size of the device as well as the voltage it requires.

“Prior to this study, it wasn’t clear that AlScN would retain the necessary ferroelectric properties while scaling down to this size,” says Olsson.

“We also found that removing the MoS2 and using AlScN in a two-terminal device geometry allows it to function as a diode-memristor-like memory device,” adds Stach. “Diode memristors are simpler than FE-FET devices and even easier to integrate on a commercial scale since they require fewer steps and components.

Jariwala and his colleagues will continue to investigate manufacturing techniques for these devices that would allow them to be mass-produced and integrated into consumer electronics.

Former postdoctoral researchers Dixiong Wang and Jinshui Miao, graduate students Kwan-Ho Kim and Jeffrey Zheng, undergraduate Keshava Katti, and current postdoctoral researcher Pariasadat Musavigharavi, all of Penn Engineering, also contributed to the research.

The research was supported by the Defense Advanced Research Projects Agency (DARPA) TUFEN program under Agreement No. HR00112090046, and the Penn Center for Undergraduate Research and Fellowships. The work was carried out in part at the Singh Center for Nanotechnology at the University of Pennsylvania, which is supported by the National Science Foundation (NSF) National Nanotechnology Coordinated Infrastructure Program through grant NNCI-1542153. Facilities and instrumentation used in the research are supported by the NSF through the University of Pennsylvania Materials Research Science and Engineering Center (MRSEC) grant DMR-1720530. Sample preparation was performed at the Center for Functional Nanomaterials, Brookhaven National Laboratory, which is a U.S. Department of Energy (DOE) Office of Science Facility, at Brookhaven National Laboratory under Contract No. DE-SC0012704.